# CoreABC v3.1

# Handbook

### Actel Corporation, Mountain View, CA 94043

© 2010 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200085-5 Release: September 2010

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### **Trademarks**

Actel, Actel Fusion, IGLOO, Libero, Pigeon Point, ProASIC, SmartFusion and the associated logos are trademarks or registered trademarks of Actel Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

|   | Introduction                             | 4  |

|---|------------------------------------------|----|

|   | CoreABC Overview                         |    |

|   | Supported Device Families                | (  |

|   | Core Version                             | (  |

|   | Supported Interfaces                     | (  |

|   | Supported Tool Flows                     | (  |

|   | Utilization and Performance              | (  |

|   |                                          |    |

| 1 | Internal Architecture                    | 1  |

| _ | m 171                                    | 1. |

| 2 | Tool Flows                               |    |

|   | Licenses                                 |    |

|   | SmartDesign                              |    |

|   | Simulation Flows                         |    |

|   | Synthesis in Libero IDE                  |    |

|   | Place-and-Route in Libero IDE            | 14 |

| 3 | CoreABC Interfaces                       | 14 |

| 5 | Overview of Interfaces                   |    |

|   | Parameters                               |    |

|   | EN DATAM Parameter                       |    |

|   | Ports                                    |    |

|   | 10165                                    | 1, |

| 4 | CoreABC Programmer's Model.              | 2  |

|   | Address Spaces                           |    |

|   | Registers                                | 22 |

|   | Instruction Set                          | 22 |

|   |                                          |    |

| 5 | CoreABC Operation.                       |    |

|   | ACM Lookup Table for Use with CoreAI     |    |

|   | Stack                                    |    |

|   | Interrupt Operation                      | 2  |

| 6 | CoreABC Configuration                    | 20 |

| O | Configurable Options                     |    |

|   | Cross-Validation of Configuration Fields |    |

|   | NVM Data Width on AFS090 Device          |    |

|   | N VIVI Data WIGHT OII AF 5090 Device     | 34 |

| 7 | CoreABC Programming.                     | 35 |

|   | Analysis                                 |    |

|   | CoreABC Instruction Modes                |    |

|   |                                          |    |

| 8 | Testbench and Simulation                 | 53 |

|   | Unit Testbench                           | 53 |

|   | System Simulation                        | 53 |

## Table of Contents

|    | Simulation Logging                                 | 54 |

|----|----------------------------------------------------|----|

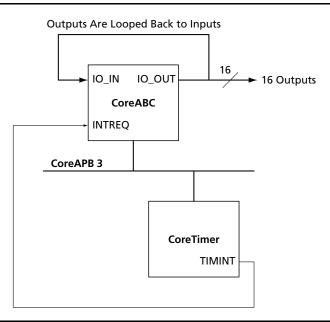

| 9  | Example Design Using CoreABC                       | 55 |

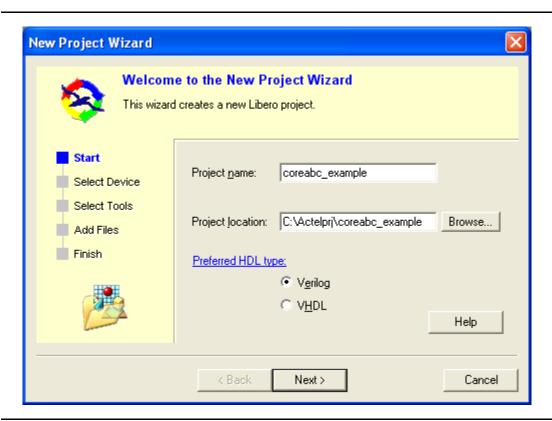

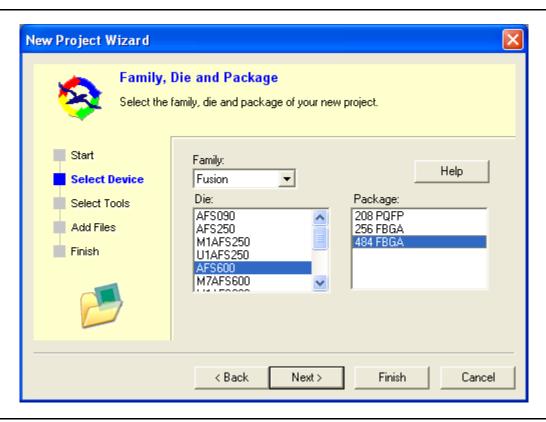

|    | Create a New Project                               | 56 |

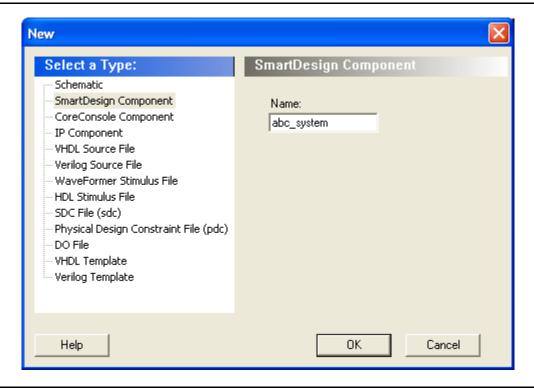

|    | Create a SmartDesign Design                        | 58 |

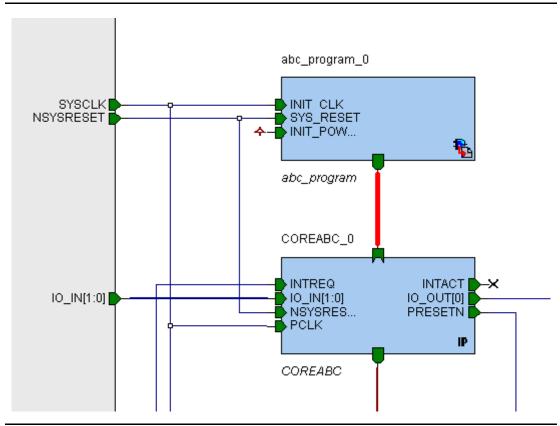

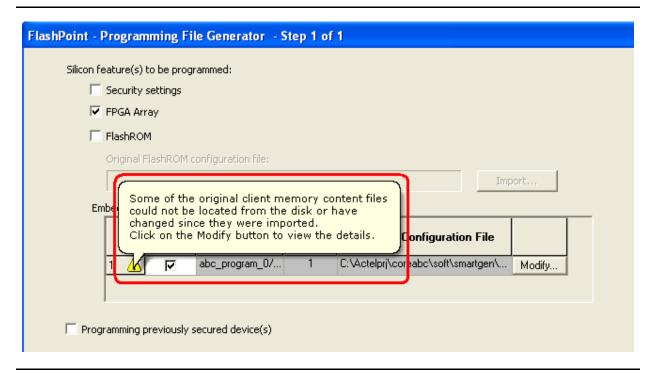

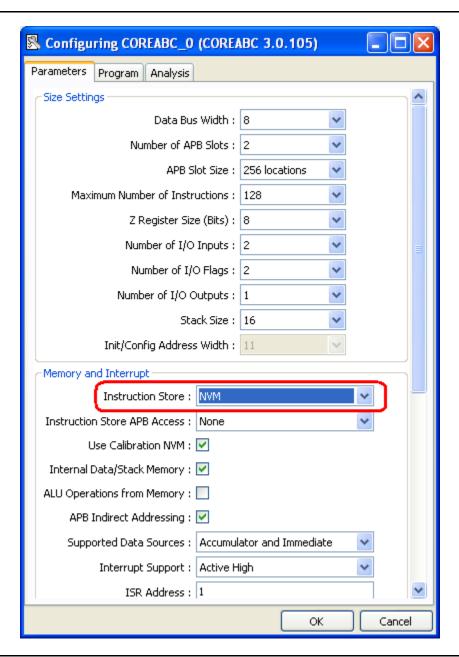

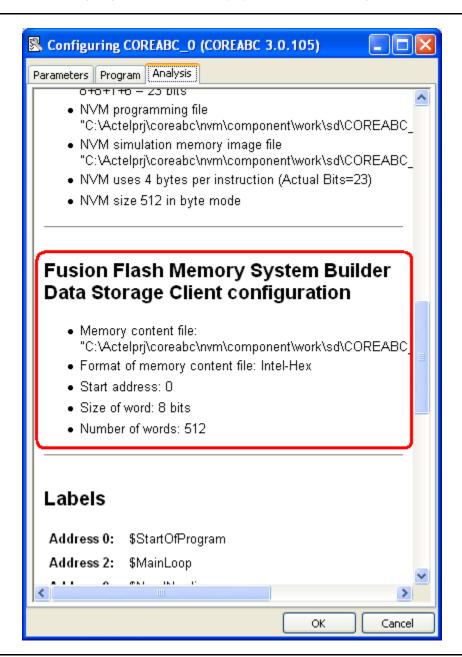

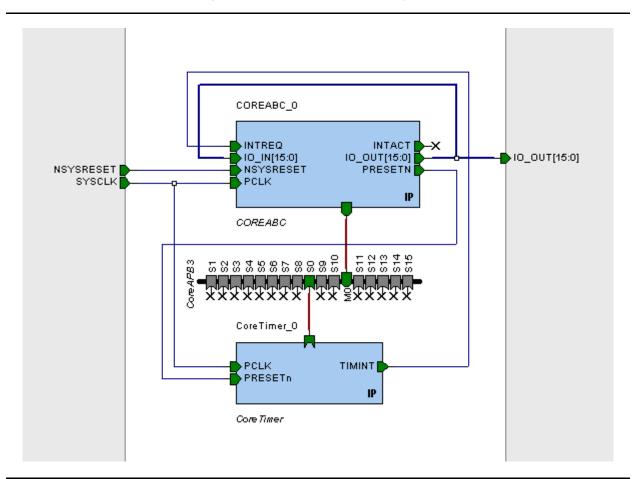

|    | Instantiate, Configure, and Connect the Components | 58 |

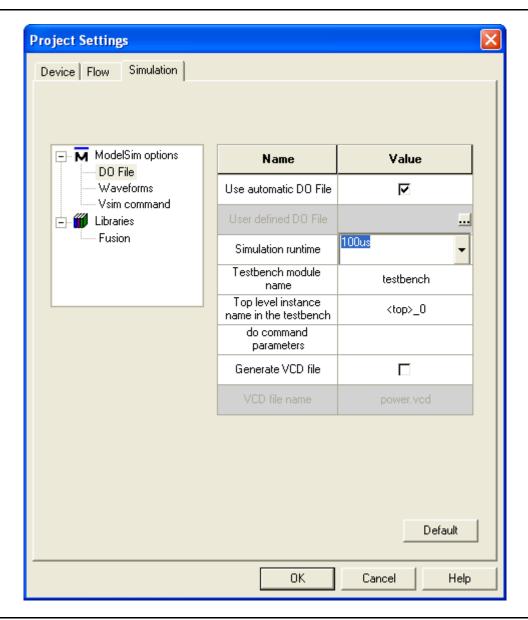

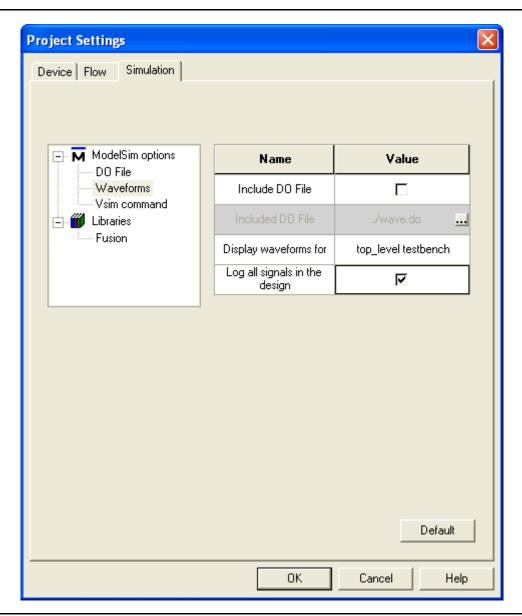

|    | System Simulation                                  | 60 |

|    | Simulation of CoreABC Only (unit test)             | 64 |

|    | Synthesis                                          | 66 |

|    | Place-and-Route                                    | 66 |

|    |                                                    |    |

| 10 | CoreABC v2.3 Migration Guide                       | 67 |

| A  | Example Instruction Sequence                       | 69 |

| R  | Instruction Summary                                | 7: |

| D  | Instructions                                       |    |

|    | Condition Codes                                    |    |

|    | Condition Codes                                    | 00 |

| C  | List of Document Changes                           | 89 |

| D  | Product Support                                    | 91 |

|    | Customer Service                                   |    |

|    | Actel Customer Technical Support Center            | 91 |

|    | Actel Technical Support                            |    |

|    | Website                                            | 91 |

|    | Contacting the Customer Technical Support Center   |    |

|    | Index                                              | 93 |

|    |                                                    |    |

# Introduction

### **CoreABC Overview**

CoreABC (ABC = APB bus controller) is a simple, configurable, low gate count, programmable state machine/controller primarily targeted toward the implementation of Advanced Microcontroller Bus Architecture (AMBA®) Advanced Peripheral Bus (APB) based designs. It is particularly suitable in the following situations:

- A programmable controller is required but a full featured CPU such as Core8051s or ARM® Cortex<sup>TM</sup>-M1 is not needed or cannot be justified due to cost or resource/size constraints.

- A full featured CPU based system requires a CoreABC based programmable offload engine/coprocessor subsystem for performance reasons.

- An Actel Fusion® system using CoreAI or CorePWM, for example, requires programmable control either as a standalone design or as a Fusion analog offload engine/coprocessor for a larger CPU based system.

CoreABC supports a comprehensive assembler based configurable instruction set architecture and extensive and flexible configuration of size and feature options, allowing it to be tuned to meet the resource constraints and processing power requirements of a wide variety of applications.

CoreABC supports three program storage modes:

- Hard mode: program image is stored in an internal ROM implemented in FPGA fabric tiles

- Soft mode: program image is stored in Actel FPGA RAM blocks which are initialized at runtime from the binary image stored in Fusion NVM or an external flash memory

- NVM mode (Fusion only): program image stored in and executed directly from Fusion NVM

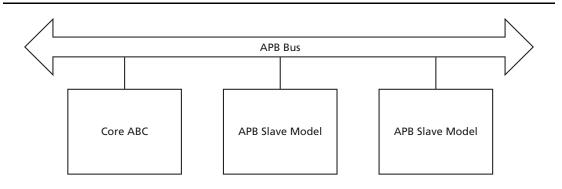

CoreABC is available through the Actel Libero<sup>®</sup> Integrated Design Environment (IDE) IP Catalog, through which it can be downloaded from a remote web-based repository and installed into the user's local vault, ready for use. It operates natively within the SmartDesign design entry environment, allowing it to be easily instantiated, configured, and connected to other IP core instances and generated ready for simulation, synthesis, etc. CoreABC is an AMBA3 APB master which can connect to and manage any APB slave peripherals via an AMBA3 APB bus fabric component such as CoreAPB3.

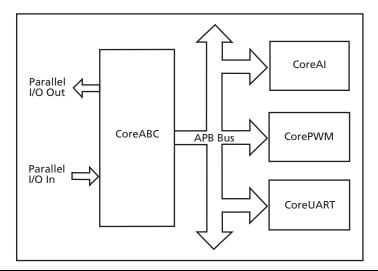

Figure 1 shows a CoreABC based system that can monitor analog inputs, adjust output levels, and report status via an RS-232 link using CoreUART.

Figure 1 • Typical CoreABC System

# **Supported Device Families**

Fusion

$\mathsf{IGLOO}^{\circledR}$

**IGLOOe**

IGLOO PLUS

ProASIC®3L

ProASIC3

ProASIC3E

ProASICPLUS

Axcelerator®

RTAX-S

### **Core Version**

This handbook supports CoreABC v3.0.

# **Supported Interfaces**

CoreABC has an AMBA3 APB master interface, which is described in "CoreABC Interfaces" on page 15.

When configured in NVM mode, an additional AMBA3 APB slave interface is available for accessing the NVM block used to store instructions within CoreABC. APB access to the instruction NVM block may be used, for example, to maintain a nonvolatile log of data values in cases where only one NVM block is available for CoreABC's use.

When configured in soft mode, an initialization and configuration (InitCfg) interface is used for initializing the RAM blocks used for CoreABC's instruction memory.

# **Supported Tool Flows**

CoreABC requires Actel Libero IDE v8.6 SP1 or later. Additionally, Verilog users MUST use Synplicity® v8.6.1 or later, which is downloadable from www.synplicity.com.

## **Utilization and Performance**

CoreABC utilization varies depending on how it is configured. Table 1 below and Table 2 on page 9 provide typical utilization data for a range of devices and data widths. The other configuration options for the core are collectively grouped to give three different CoreABC configurations named small, medium, and large; these configurations are listed in Table 3-1 on page 15. CoreABC can be implemented in several Actel FPGA devices.

Table 1 • CoreABC Utilization Data (Hard Mode—instructions held in tiles)

| Family                                          | Data<br>Width | Config. | Comb. | Seq. | RAM | Total | Device                     | Utilization | Frequency<br>MHz* |

|-------------------------------------------------|---------------|---------|-------|------|-----|-------|----------------------------|-------------|-------------------|

| Fusion<br>ProASIC®3/E<br>IGLOO <sup>TM</sup> /e | 8             | Small   | 179   | 46   | 0   | 225   | AFS600<br>A3P600<br>AGL600 | 1.6%        | 92                |

| ProASICPLUS                                     | 8             | Small   | 195   | 51   | 0   | 246   | APA450                     | 2.0%        | 81                |

| Axcelerator®<br>RTAX-S                          | 8             | Small   | 96    | 45   | 0   | 141   | AX250<br>RTAX250           | 3.3%        | 123               |

Table 1 • CoreABC Utilization Data (Hard Mode—instructions held in tiles) (continued)

| Family                          | Data<br>Width | Config. | Comb. | Seq. | RAM | Total | Device                     | Utilization | Frequency<br>MHz* |

|---------------------------------|---------------|---------|-------|------|-----|-------|----------------------------|-------------|-------------------|

| Fusion<br>ProASIC3/E<br>IGLOO/e | 16            | Small   | 238   | 59   | 0   | 297   | AFS600<br>A3P600<br>AGL600 | 2.1%        | 79                |

| ProASICPLUS                     | 16            | Small   | 269   | 63   | 0   | 332   | APA450                     | 2.7%        | 79                |

| Axcelerator<br>RTAX-S           | 16            | Small   | 127   | 57   | 0   | 184   | AX250<br>RTAX250           | 4.4%        | 98                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 32            | Small   | 319   | 74   | 0   | 393   | AFS600<br>A3P600<br>AGL600 | 2.8%        | 58                |

| ProASICPLUS                     | 32            | Small   | 381   | 84   | 0   | 465   | APA450                     | 3.9%        | 60                |

| Axcelerator<br>RTAX-S           | 32            | Small   | 192   | 78   | 0   | 270   | AX250<br>RTAX250           | 6.4%        | 97                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 8             | Medium  | 363   | 76   | 1   | 439   | AFS600<br>A3P600<br>AGL600 | 3.2%        | 55                |

| ProASICPLUS                     | 8             | Medium  | 439   | 88   | 1   | 527   | APA450                     | 4.3%        | 41                |

| Axcelerator<br>RTAX-S           | 8             | Medium  | 229   | 76   | 1   | 305   | AX250<br>RTAX250           | 7.2%        | 86                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 16            | Medium  | 558   | 88   | 1   | 646   | AFS600<br>A3P600<br>AGL600 | 4.7%        | 41                |

| ProASICPLUS                     | 16            | Medium  | 630   | 95   | 2   | 725   | APA450                     | 5.9%        | 32                |

| Axcelerator<br>RTAX-S           | 16            | Medium  | 307   | 92   | 1   | 399   | AX250<br>RTAX250           | 9.4%        | 73                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 32            | Medium  | 896   | 104  | 2   | 1,000 | AFS600<br>A3P600<br>AGL600 | 7.2%        | 37                |

| ProASICPLUS                     | 32            | Medium  | 947   | 112  | 4   | 1,059 | APA450                     | 8.6%        | 28                |

| Axcelerator<br>RTAX-S           | 32            | Medium  | 442   | 108  | 2   | 550   | AX250<br>RTAX250           | 13.0%       | 64                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 8             | Large   | 474   | 82   | 1   | 556   | AFS600<br>A3P600<br>AGL600 | 4.0%        | 42                |

| ProASIC PLUS                    | 8             | Large   | 565   | 94   | 1   | 659   | APA450                     | 5.4%        | 38                |

| Axcelerator<br>RTAX-S           | 8             | Large   | 291   | 86   | 1   | 377   | AX250<br>RTAX250           | 8.9%        | 71                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 16            | Large   | 648   | 94   | 1   | 742   | AFS600<br>A3P600<br>AGL600 | 5.4%        | 27                |

| ProASIC <u>PLUS</u>             | 16            | Large   | 763   | 105  | 2   | 868   | APA450                     | 7.1%        | 24                |

Table 1 • CoreABC Utilization Data (Hard Mode—instructions held in tiles) (continued)

| Family                          | Data<br>Width | Config. | Comb. | Seq. | RAM | Total | Device                     | Utilization | Frequency<br>MHz* |

|---------------------------------|---------------|---------|-------|------|-----|-------|----------------------------|-------------|-------------------|

| Axcelerator<br>RTAX-S           | 16            | Large   | 399   | 98   | 1   | 497   | AX250<br>RTAX250           | 11.8%       | 69                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 32            | Large   | 1,014 | 111  | 2   | 1,125 | AFS600<br>A3P600<br>AGL600 | 8.1%        | 34                |

| ProASICPLUS                     | 32            | Large   | 1,082 | 126  | 4   | 1,208 | APA450                     | 9.8%        | 18                |

| Axcelerator<br>RTAX-S           | 32            | Large   | 586   | 119  | 2   | 705   | AX250<br>RTAX250           | 16.7%       | 53                |

Table 2 • CoreABC Utilization Data (Soft Mode—instructions held in RAM)

| Family                          | Data<br>Width | Config. | Comb. | Seq. | RAM | Total | Device                     | Utilization | Frequency<br>MHz* |

|---------------------------------|---------------|---------|-------|------|-----|-------|----------------------------|-------------|-------------------|

| Fusion<br>ProASIC3/E<br>IGLOO/e | 8             | Small   | 126   | 27   | 3   | 153   | AFS600<br>A3P600<br>AGL600 | 1.1%        | 68                |

| ProASICPLUS                     | 8             | Small   | 137   | 30   | 6   | 167   | APA450                     | 1.4%        | 53                |

| Axcelerator<br>RTAX-S           | 8             | Small   | 61    | 27   | 3   | 88    | AX250<br>RTAX250           | 2.1%        | 95                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 16            | Small   | 179   | 36   | 4   | 215   | AFS600<br>A3P600<br>AGL600 | 1.6%        | 67                |

| ProASICPLUS                     | 16            | Small   | 213   | 41   | 8   | 254   | APA450                     | 2.1%        | 50                |

| Axcelerator<br>RTAX-S           | 16            | Small   | 94    | 35   | 4   | 129   | AX250<br>RTAX250           | 3.1%        | 84                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 32            | Small   | 353   | 53   | 5   | 406   | AFS600<br>A3P600<br>AGL600 | 2.9%        | 46                |

| ProASICPLUS                     | 32            | Small   | 359   | 58   | 10  | 417   | APA450                     | 3.4%        | 42                |

| Axcelerator<br>RTAX-S           | 32            | Small   | 155   | 52   | 5   | 207   | AX250<br>RTAX250           | 4.9%        | 65                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 8             | Medium  | 326   | 56   | 4   | 382   | AFS600<br>A3P600<br>AGL600 | 2.8%        | 46                |

| ProASICPLUS                     | 8             | Medium  | 409   | 59   | 7   | 468   | APA450                     | 3.8%        | 34                |

| Axcelerator<br>RTAX-S           | 8             | Medium  | 210   | 55   | 4   | 265   | AX250<br>RTAX250           | 6.3%        | 59                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 16            | Medium  | 548   | 64   | 5   | 612   | AFS600<br>A3P600<br>AGL600 | 4.4%        | 40                |

| ProASICPLUS                     | 16            | Medium  | 659   | 73   | 10  | 732   | APA450                     | 6.0%        | 28                |

| Axcelerator<br>RTAX-S           | 16            | Medium  | 271   | 64   | 5   | 335   | AX250<br>RTAX250           | 7.9%        | 58                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 32            | Medium  | 851   | 80   | 8   | 931   | AFS600<br>A3P600<br>AGL600 | 6.7%        | 32                |

| ProASICPLUS                     | 32            | Medium  | 892   | 96   | 16  | 988   | APA450                     | 8.0%        | 26                |

| Axcelerator<br>RTAX-S           | 32            | Medium  | 399   | 80   | 8   | 479   | AX250<br>RTAX250           | 11.3%       | 50                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 8             | Large   | 462   | 62   | 5   | 524   | AFS600<br>A3P600<br>AGL600 | 3.8%        | 40                |

Table 2 • CoreABC Utilization Data (Soft Mode—instructions held in RAM) (continued)

| Family                          | Data<br>Width | Config. | Comb. | Seq. | RAM | Total | Device                     | Utilization | Frequency<br>MHz* |

|---------------------------------|---------------|---------|-------|------|-----|-------|----------------------------|-------------|-------------------|

| ProASIC PLUS                    | 8             | Large   | 534   | 67   | 9   | 601   | APA450                     | 4.9%        | 31                |

| Axcelerator<br>RTAX-S           | 8             | Large   | 282   | 61   | 5   | 343   | AX250<br>RTAX250           | 8.1%        | 63                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 16            | Large   | 626   | 71   | 6   | 697   | AFS600<br>A3P600<br>AGL600 | 5.0%        | 25                |

| ProASICPLUS                     | 16            | Large   | 732   | 83   | 12  | 815   | APA450                     | 6.6%        | 21                |

| Axcelerator<br>RTAX-S           | 16            | Large   | 380   | 70   | 6   | 450   | AX250<br>RTAX250           | 10.7%       | 56                |

| Fusion<br>ProASIC3/E<br>IGLOO/e | 32            | Large   | 1,053 | 86   | 8   | 1,139 | AFS600<br>A3P600<br>AGL600 | 8.2%        | 34                |

| ProASIC PLUS                    | 32            | Large   | 1,228 | 106  | 16  | 1,334 | APA450                     | 10.9%       | 27                |

| Axcelerator<br>RTAX-S           | 32            | Large   | 579   | 85   | 8   | 664   | AX250<br>RTAX250           | 15.7%       | 46                |

# 1 – Internal Architecture

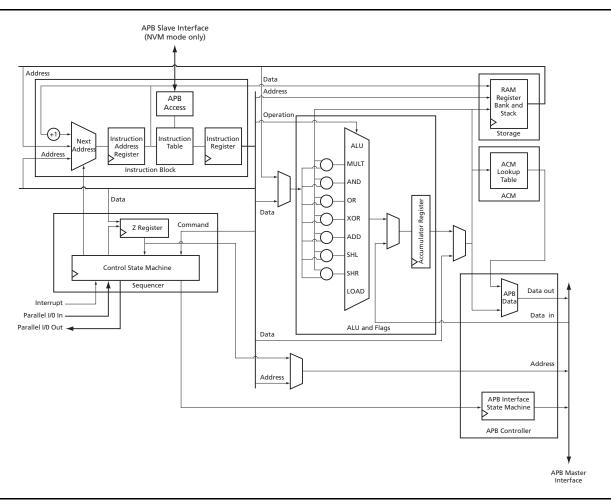

CoreABC internal architecture is shown in Figure 1-1. The core consists of six main blocks:

- · Instruction block

- · Sequencer

- · ALU and Flags

- Storage

- Analog configuration MUX (ACM)

- APB controller

Figure 1-1 • CoreABC Block Diagram

The Instruction block contains the instruction counter and the instruction table that contains the instructions to be executed. In soft mode, these instructions are fetched from RAM internal to CoreABC.

The ALU and Flags block implements the main ALU block. Each of the supported operations can be disabled to obtain a minimal-gate-count solution. The Storage block provides local storage for data values and implements the stack required by the call instruction.

The ACM block implements a small lookup table that can be initialized with the configuration data required by CoreAI. This allows the analog functions within a Fusion FPGA to be easily configured.

### Internal Architecture

The APB controller implements an AMBA3 APB master interface for controlling both AMBA3 and AMBA2 APB peripherals. Typically a number of APB peripherals will be in use and in such cases the CoreAPB3 bus interface core should be used to connect the various APB cores to CoreABC's master APB interface. Finally, the Sequencer controls the operation of the core, decoding of the instructions and enabling of the other blocks.

To keep tile counts low, all unused functions within CoreABC can be removed during synthesis by configuring the core appropriately.

# 2 – Tool Flows

## Licenses

CoreABC is licensed in two ways: Obfuscated and RTL. Tool flow functionality may be limited, depending on your license

### **Obfuscated**

Complete RTL code is provided for the core, enabling the core to be instantiated, configured, and generated within SmartDesign. Simulation, Synthesis, and Layout can be performed with Actel Libero Integrated Design Environment (IDE). The RTL code for the core is obfuscated.

### **RTL**

Complete RTL source code is provided for the core.

# **SmartDesign**

CoreABC is available for download to the SmartDesign IP Catalog via the Libero IDE web repository. For information on using SmartDesign to instantiate, configure, connect, and generate cores, refer to the Libero IDE online help.

The APB master interface of CoreABC will typically be connected to the mirrored master interface of CoreAPB3, with various APB slaves connected to the slave interfaces of CoreAPB3.

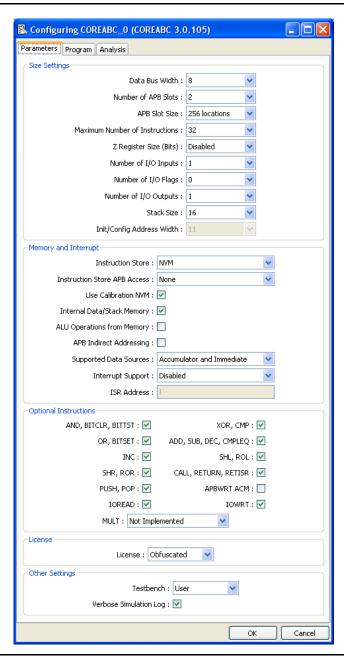

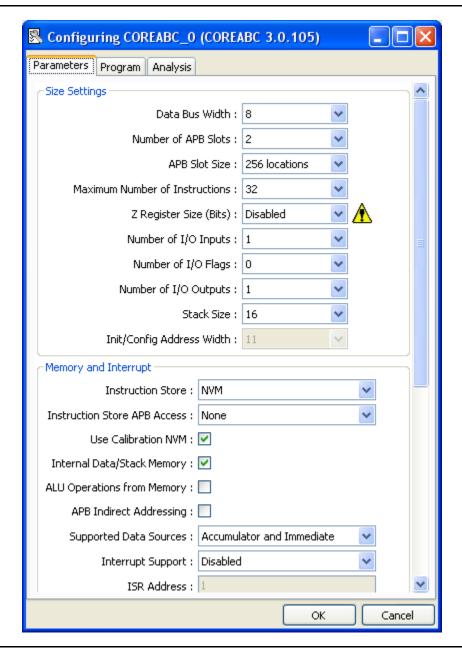

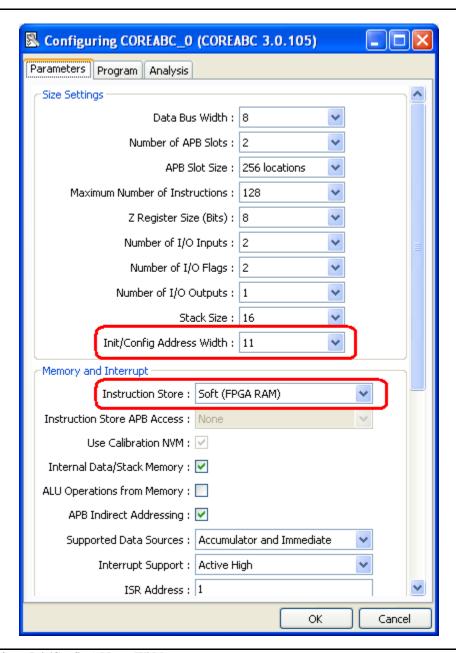

The core can be configured using the configuration GUI within SmartDesign. See the "CoreABC Configuration" section on page 29 for more details on configuring CoreABC.

## **Simulation Flows**

SmartDesign and Libero IDE facilitate running both a user (or unit) testbench for CoreABC and a basic system testbench for the complete SmartDesign design. You may wish to expand on these simulation capabilities to suit the particular needs of your project. For example, you could make a copy of the system testbench, add additional code to monitor or interact with the design and then use this new testbench as stimulus in a simulation.

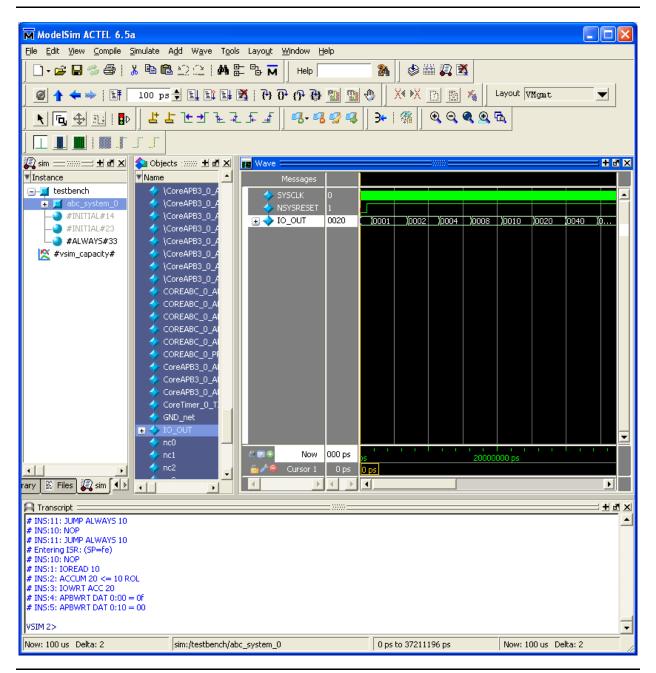

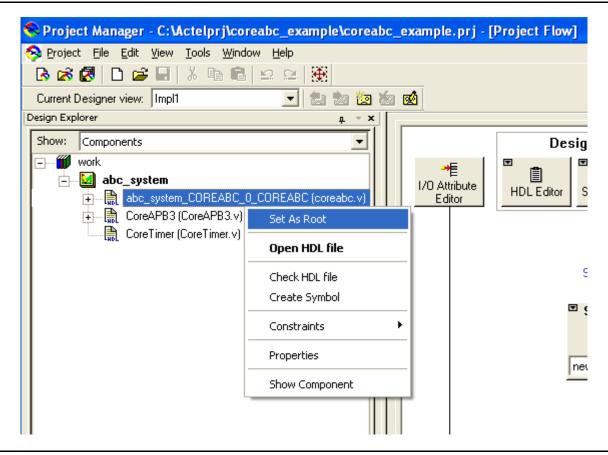

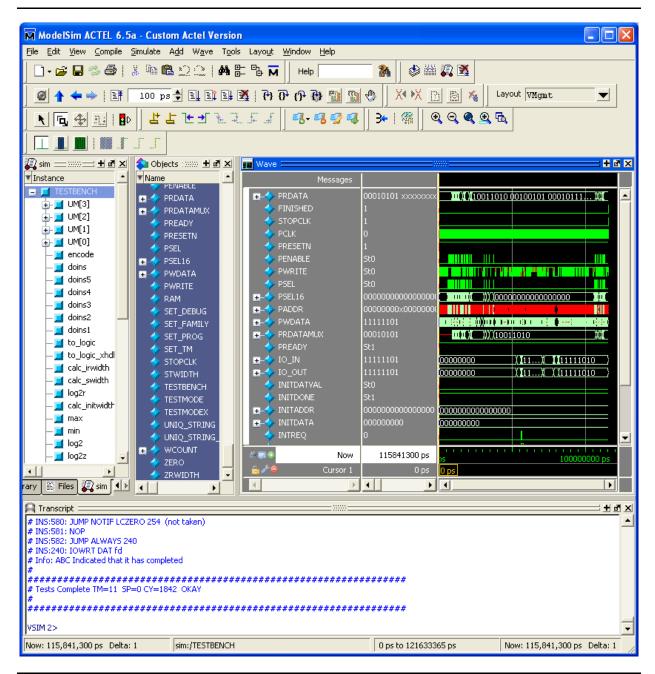

To run the CoreABC unit testbench, set the Testbench configuration option to User in the CoreABC configuration GUI before generating the design. After generation, set the design root to be the CoreABC instance and click the Simulation (ModelSim) button. ModelSim will launch and run the unit test.

To run the system testbench for the SmartDesign design, set the design root to be the (SmartDesign) design after generation and again click the **Simulation** button. ModelSim will launch and run the system simulation.

See "Testbench and Simulation" on page 53 for more details on simulation.

# **Synthesis in Libero IDE**

To run synthesis with the configuration selected in the configuration GUI, set the design root appropriately and click the **Synthesis** icon in Libero IDE to launch the Synplicity<sup>®</sup> synthesis tool. Click the **Run** button in the synthesis window to run synthesis.

# Place-and-Route in Libero IDE

Having set the design route appropriately and run Synthesis, click the **Place&Route** icon in Libero IDE to invoke Designer. CoreABC requires no special place-and-route settings.

# 3 - CoreABC Interfaces

## **Overview of Interfaces**

CoreABC has an AMBA3 APB master interface which typically will be connected to CoreAPB3. When in NVM mode (INSMODE parameter set to 2), an additional AMBA3 APB slave interface is available for data type access to the (NVM) instruction store.

Note: When CoreABC is mastering CoreAPB3, the APB Slot Size configuration option settings should match for both of these cores.

In soft mode (INSMODE parameter set to 1), an initialization and configuration (InitCfg) interface is available for initializing the RAM blocks used as CoreABC's instruction store. This interface is intended to be used to connect to a Flash Memory System Builder (FMSB) RAM Initialization client. The use of FMSB clients is supported only on Fusion devices. On other device families, a different means must be employed to initialize the instruction RAM blocks through the InitCfg interface. This could involve implementing some logic to allow another processor in the system to communicate with the InitCfg interface.

In addition to the interfaces already mentioned, CoreABC has clock, reset, and interrupt related signals as well as general purpose parallel input and output buses. The widths of these input and output buses are configurable.

## **Parameters**

The parameters described are those directly in the RTL. When working with CoreABC in the SmartDesign tool, a configuration GUI is available for setting these parameters. The recommended configuration flow is to use the configuration GUI in SmartDesign, which will then set these parameters correctly. Importantly, when using the configuration GUI, the parameter settings will be cross checked with the CoreABC program (which is entered in another tab of the configuration GUI). The configuration GUI will indicate any inconsistencies between the program and the parameter settings. See "CoreABC Configuration" on page 29 for more information on the configuration GUI.

Table 3-1 • CoreABC Parameters

|            |              |                                                                                                                                                              | Value     |           |           |  |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|--|

| Parameter  | Values       | Description                                                                                                                                                  | Small     | Medium    | Large     |  |

| APB_AWIDTH | 8 to 16      | Sets the width of the APB address bus.                                                                                                                       | 8         | 8         | 8         |  |

| APB_DWIDTH | 8, 16, or 32 | Sets the width of the APB data bus.                                                                                                                          | 8, 16, 32 | 8, 16, 32 | 8, 16, 32 |  |

| APB_SDEPTH | 1 to 16      | Sets the number of supported APB devices.                                                                                                                    | 1         | 4         | 16        |  |

| ICWIDTH    | 1 to 16      | Sets the maximum number of supported instructions. Number of allowed instructions is $2^{ICWIDTH}$ . ICWIDTH must be $\leq$ APB_AWIDTH.                      | 5         | 8         | 8         |  |

| ZRWIDTH    | 0 to 16      | Sets the width of the Z register. A setting of 8 would allow for a maximum value of 2 <sup>8</sup> (i.e., 256). Zero will disable and remove the Z register. | 0         | 8         | 8         |  |

| IIWIDTH    | 1 to 32      | Sets the width of the IO_IN input. IIWIDTH must be $\leq$ APB_DWIDTH.                                                                                        | 1         | 4         | 4         |  |

| IFWIDTH    | 1 to 28      | Sets how many of the IO_IN bits can be used with the conditional instructions. IFWIDTH must be ≤ APB_DWIDTH – 4.                                             |           |           |           |  |

| IOWIDTH    | 1 to 32      | Sets the width of the IO_OUT output. IOWIDTH must be $\leq$ APB_DWIDTH.                                                                                      | 1         | 8         | 8         |  |

Table 3-1 • CoreABC Parameters (continued)

|             |             |                                                                                                                                                                                                                                                                                                          | Value |        |       |  |

|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|--|

| Parameter   | Values      | Description                                                                                                                                                                                                                                                                                              | Small | Medium | Large |  |

| STWIDTH     | 1 to 8      | Sets the size of the internal stack counter used to support the call instruction and interrupt function. The depth of the stack is $2^{\text{STWIDTH}}$ .                                                                                                                                                | 1     | 4      | 4     |  |

| EN_RAM      | 0 or 1      | When 1, a RAM block is used in the core to provide 256 storage locations. This RAM is also used to store return addresses for the call and interrupt functions.                                                                                                                                          | 0     | 1      | 1     |  |

| EN_AND      | 0 or 1      | When 1, the ALU supports the AND function.                                                                                                                                                                                                                                                               | 1     | 1      | 1     |  |

| EN_XOR      | 0 or 1      | When 1, the ALU supports the XOR function.                                                                                                                                                                                                                                                               | 1     | 1      | 1     |  |

| EN_OR       | 0 or 1      | When 1, the ALU supports the OR function.                                                                                                                                                                                                                                                                | 0     | 1      | 1     |  |

| EN_ADD      | 0 or 1      | When 1, the ALU supports the ADD function.                                                                                                                                                                                                                                                               | 0     | 1      | 1     |  |

| EN_INC      | 0 or 1      | When 1, the ALU supports the INC function.                                                                                                                                                                                                                                                               | 0     | 1      | 1     |  |

| EN_SHL      | 0 or 1      | When 1, the ALU supports the SHL/ROL function.                                                                                                                                                                                                                                                           | 0     | 1      | 1     |  |

| EN_SHR      | 0 or 1      | When 1, the ALU supports the SHR/ROR function.                                                                                                                                                                                                                                                           | 0     | 1      | 1     |  |

| EN_CALL     | 0 or 1      | When 1, the core supports the call and return operations.                                                                                                                                                                                                                                                | 0     | 1      | 1     |  |

| EN_PUSH     | 0 or 1      | When 1, the core supports the push and pop operations.                                                                                                                                                                                                                                                   | 0     | 1      | 1     |  |

| EN_ACM      | 0 or 1      | When 1, enables the ACM initialization table.                                                                                                                                                                                                                                                            | 0     | 1      | 1     |  |

| EN_DATAM    | 0 to 3      | Controls internal multiplexing; see "EN_DATAM Parameter" on page 18.                                                                                                                                                                                                                                     | 1     | 1      | 1     |  |

| EN_INT      | 0 to 2      | Enables the external interrupt function. When 0, interrupts are disabled. When 1, INTREQ is active high. When 2, INTREQ is active low.                                                                                                                                                                   | 0     | 1      | 1     |  |

| EN_MULT     | 0 to 3      | Enables the hardware multiplier; four options exist (example for 16-bit core):  0: No hardware multiplier  1: Half multiplier, P(15:0) <= A(7:0) * B(7:0)  2: Full multiplier returning lower half, P(15:0) <= A(15:0) * B(15:0)  3: Full multiplier returning upper half, P(31:16) <= A(15:0) * B(15:0) | 0     | 0      | 0     |  |

| EN_IOREAD   | 0 or 1      | When 1, the IOREAD instruction is enabled.                                                                                                                                                                                                                                                               | 0     | 1      | 1     |  |

| EN_IOWRT    | 0 or 1      | When 1, the IOWRT instruction is enabled.                                                                                                                                                                                                                                                                | 1     | 1      | 1     |  |

| EN_ALURAM   | 0 or 1      | When 1, the Boolean and Arithmetic instructions can operate on memory contents.                                                                                                                                                                                                                          | 0     | 1      | 1     |  |

| EN_INDIRECT | 0 or 1      | When 1, the Z register can be used to generate the APB address, and the APBWRTZ and APBREADZ instructions are enabled.                                                                                                                                                                                   | 0     | 0      | 1     |  |

| ISRADDR     | 0 to 65,535 | The address CoreABC should jump to when responding to an interrupt request.                                                                                                                                                                                                                              | 0     | 220    | 220   |  |

Table 3-1 • CoreABC Parameters (continued)

|                     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Value |        |       |

|---------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|

| Parameter           | Values   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Small | Medium | Large |

| INSMODE             | 0 to 2   | When 0, the instructions are contained in internal logic gates, implementing a ROM function. When 1, internal RAM blocks are used to hold the instruction sequence. When 2, internal NVM is used to hold the instruction sequence. INSMODE = 2 is supported only on Fusion devices.                                                                                                                                                                                                         | 0     | 0      | 1     |

| ACT_CALIBRATIONDATA | 0 or 1   | When 1, the NVM block containing the calibration data for the device is selected if INSMODE = 2. When 0, any available NVM block may be used. This option is only applicable when INSMODE = 2, which implies that a Fusion device is being used.                                                                                                                                                                                                                                            | N/A   | N/A    | N/A   |

| IMEM_APB_ACCESS     | 0 to 2   | When 0, APB access to instruction memory is not supported. When 1, read only APB access to instruction memory is possible. When 2, read and write APB access to instruction memory is supported.                                                                                                                                                                                                                                                                                            | N/A   | N/A    | N/A   |

| INITWIDTH           | 1 to 16  | Specifies the width of the INITADDR input used to initialize the instruction RAM blocks when INSMODE = 1. The actual width depends on several generic values. Utilities used to support soft operation calculate this value.                                                                                                                                                                                                                                                                | 0     | 0      | 16    |

| DEBUG               | 0 or 1   | When 1 during simulation, a detailed log will be generated of the internal operation.                                                                                                                                                                                                                                                                                                                                                                                                       | N/A   | N/A    | N/A   |

| TESTMODE            | 0 to 16  | Selects a predefined set of instructions used for core verification. This should be set to 0 unless the verification test sequences are being used.                                                                                                                                                                                                                                                                                                                                         | N/A   | N/A    | N/A   |

| UNIQ_STRING_LENGTH  | 0 to 256 | This parameter gives the length (number of characters) of the unique string which is derived from the instance name of a particular CoreABC instance. This parameter forms part of the mechanism which allows multiple instances of CoreABC to be easily used in a single design.                                                                                                                                                                                                           | N/A   | N/A    | N/A   |

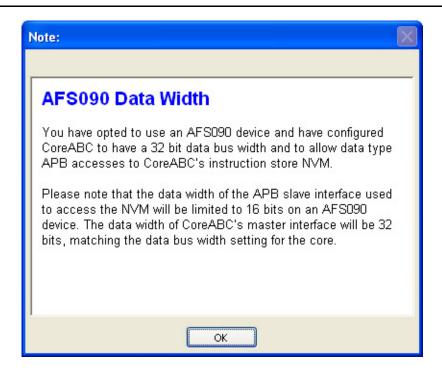

| MAX_NVMDWIDTH       | 16 or 32 | Indicates the maximum bit width supported on the data buses connecting to any NVM macro within CoreABC. This parameter is only applicable when CoreABC is configured to operate in NVM mode which is only possible for a Fusion device. This parameter is not directly controllable from the configuration GUI but is instead automatically set to match the target device. A setting of 16 is applied when an AFS090 device is targeted. For all other devices the parameter is set to 32. | N/A   | N/A    | N/A   |

# **EN\_DATAM Parameter**

This allows various internal multiplexers to be optimized out of the core, lowering tile counts. The settings supported are given in Table 3-2 through Table 3-5 on page 18, and the tables show which instructions are allowed with each setting.

Table 3-2 • Accumulator Only (EN\_DATAM = 0)

|        | Immediate Data | Accumulator |

|--------|----------------|-------------|

| APBWRT | No             | Yes + ACM   |

| RAMWRT | No             | Yes         |

| PUSH   | No             | Yes         |

| LOADZ  | No             | Yes         |

| IOWRT  | No             | Yes         |

### **Table 3-3** • Immediate Only (EN\_DATAM = 1)

|        | Immediate Data | Accumulator |

|--------|----------------|-------------|

| APBWRT | Yes            | No          |

| RAMWRT | Yes            | No          |

| PUSH   | Yes            | No          |

| LOADZ  | Yes            | No          |

| IOWRT  | Yes            | No          |

## **Table 3-4** • Accumulator and Immediate (EN\_DATAM = 2)

|        | Immediate Data | Accumulator |

|--------|----------------|-------------|

| APBWRT | Yes            | Yes + ACM   |

| RAMWRT | Yes            | Yes         |

| LOADZ  | Yes            | Yes         |

| PUSH   | Yes            | Yes         |

| IOWRT  | Yes            | Yes         |

## *Table 3-5* • Instruction-Dependent (EN\_DATAM = 3)

|        | Immediate Data | Accumulator |

|--------|----------------|-------------|

| APBWRT | No             | Yes + ACM   |

| RAMWRT | No             | Yes         |

| PUSH   | No             | Yes         |

| LOADZ  | Yes            | No          |

| IOWRT  | Yes            | No          |

# **Ports**

All CoreABC inputs are sampled, and outputs clocked, on the rising edge of PCLK.

**Table 3-6** • CoreABC Port Descriptions

| Name          | Type | Description                                                                                                                                                                                                                                                                                                                                         |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK          | In   | Clock input                                                                                                                                                                                                                                                                                                                                         |

| NSYSRESET     | In   | Reset input (asynchronous active low)                                                                                                                                                                                                                                                                                                               |

| PRESETN       | Out  | Reset output; synchronized version of NSYSRESET                                                                                                                                                                                                                                                                                                     |

| PENABLE_M     | Out  | APB master interface enable signal                                                                                                                                                                                                                                                                                                                  |

| PWRITE_M      | Out  | APB master interface write signal                                                                                                                                                                                                                                                                                                                   |

| PSEL_M        | Out  | APB master interface select signal                                                                                                                                                                                                                                                                                                                  |

| PADDR_M[19:0] | Out  | APB master interface address bus. The width of this address bus is fixed at 20 bits but some of the upper bits may not be significant, depending on the configuration of the core. The number of significant bits is determined by the APB_AWIDTH and the APB_SDEPTH parameters. Number of significant bits = APB_AWIDTH + log base 2 (APB_SDEPTH). |

| PWDATA_M[x:0] | Out  | APB master interface write data bus. The width is controlled by APB_DWIDTH.                                                                                                                                                                                                                                                                         |

| PRDATA_M[x:0] | In   | APB master interface read data bus. The width is controlled by APB_DWIDTH.                                                                                                                                                                                                                                                                          |

| PREADY_M      | In   | APB master interface ready input.                                                                                                                                                                                                                                                                                                                   |

| PSLVERR_M     | In   | APB master interface slave error signal. This input currently is not used by CoreABC.                                                                                                                                                                                                                                                               |

| IO_IN[x:0]    | In   | General-purpose inputs. The width is controlled by IIWIDTH.                                                                                                                                                                                                                                                                                         |

| IO_OUT[x:0]   | Out  | General-purpose outputs. The width is controlled by IOWIDTH.                                                                                                                                                                                                                                                                                        |

| INTREQ        | In   | Interrupt request input. When this input is asserted, the instruction sequence will jump to the address set by the ISRADDR parameter.                                                                                                                                                                                                               |

| INTACT        | Out  | Indicates that the core has entered the interrupt service routine.                                                                                                                                                                                                                                                                                  |

| INITDATAVAL   | In   | Enable signal (active high) indicating that the INITADDR and INITDATA inputs are valid. When using a SmartGen initialization client, this signal connects to the client select signal.                                                                                                                                                              |

| INITDONE      | In   | Indicates that initialization has been completed (active high) and the core should start operating.                                                                                                                                                                                                                                                 |

| INITADDR[x:0] | In   | Connects to the INITADDR output of the INITCFG block used to configure the RAM blocks when INSMODE = 1. When INSMODE = 0, these inputs should be tied to logic 0. The width of this input is controlled by the INITWIDTH generic.                                                                                                                   |

| INITDATA[8:0] | In   | Connects to the INITDATA output of the INITCFG block, used to configure the RAM blocks when $INSMODE = 1$ . When $INSMODE = 0$ , these inputs should be tied to logic 0.                                                                                                                                                                            |

| PSEL_S        | In   | Select signal of APB slave interface used to access instruction memory in NVM mode                                                                                                                                                                                                                                                                  |

| PENABLE_S     | In   | Enable signal of APB slave interface used to access instruction memory in NVM mode                                                                                                                                                                                                                                                                  |

| PWRITE_S      | In   | Write signal of APB slave interface used to access instruction memory in NVM mode.                                                                                                                                                                                                                                                                  |

| PADDR_S[x:0]  | In   | Address bus of APB slave interface used to access instruction memory in NVM mode. Width is determined by APB_AWIDTH.                                                                                                                                                                                                                                |

| PWDATA_S[x:0] | In   | Write data bus of APB slave interface used to access instruction memory in NVM mode. Width is determined by APB_DWIDTH.                                                                                                                                                                                                                             |

| PRDATA_S[x:0] | Out  | Read data bus of APB slave interface used to access instruction memory in NVM mode. Width is determined by APB_DWIDTH.                                                                                                                                                                                                                              |

CoreABC Interfaces

Table 3-6 • CoreABC Port Descriptions (continued)

| Name      | Type | Description                                                                        |  |

|-----------|------|------------------------------------------------------------------------------------|--|

| PSLVERR_S | Out  | Error signal of APB slave interface used to access instruction memory in NVM mode. |  |

| PREADY_S  | Out  | Ready signal of APB slave interface used to access instruction memory in NVM mode. |  |

# 4 - CoreABC Programmer's Model

CoreABC is an accumulator based load/store architecture with multiple independent memory spaces. It is effectively a Harvard architecture (independent instruction and data address spaces). Most instructions act only on the accumulator, but there are specific instructions to access the memory spaces described below.

# **Address Spaces**

The instruction address space is linear and is implemented as a hard-coded instruction table (hard mode), or an internal instruction RAM (soft mode), or an internal NVM block (NVM mode). This is implicitly accessed by control transfer instructions such as JUMP and CALL, but it cannot be directly read or written otherwise, except in the case where APB read/write data type access to instruction memory is enabled in NVM mode. In NVM mode, if APB data type read/write access to the instruction memory is enabled, it is possible to modify or overwrite CoreABC's program. Normally you will not want to do this and you must take care to ensure that the CoreABC program does not unintentionally corrupt itself. In practice this usually just means setting the SECTOR, PAGE, and SPARE\_PAGE registers in the APB interface to NVM instruction memory to sufficiently high values. That is, read and write data type accesses to the NVM instruction memory should normally be to a region of the NVM above the program which is located from address 0x0000 onwards. See the "APB Access to Instruction Memory" section on page 51 for more details.

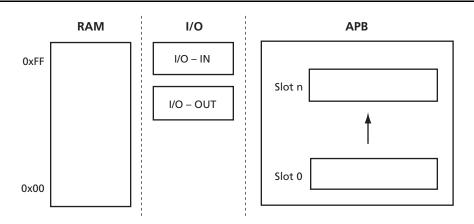

The data address spaces are shown in Figure 4-1. There are three separate, independent addressable areas. These are accessed by using instructions or instruction modes unique to each one.

Figure 4-1 • CoreAPB Data Address Spaces

## **Internal Data RAM Address Space (optional)**

This is an optional internal 256-location RAM storage area. It can be accessed directly using the RAMREAD and RAMWRT instructions, and implicitly using the PUSH and POP instructions (the stack, if one is present, is located at the top of RAM). The ALU instructions can also source the secondary operand from the RAM storage area. The width of each RAM location is equal to the data width of the processor (APB\_DWIDTH) or the width of the instruction counter (ICWIDTH), whichever is greater.

## I/O Address Space

This is a general-purpose input/output area that is accessed by IOREAD (to load the accumulator from the input) or IOWRT (to write the accumulator to the output) and the INPUTn test instructions (to read the inputs—for example, JUMP IF INPUT3).

### **APB Address Space**

The APB master interface of CoreABC typically will be connected to CoreAPB3 to provide access to up to 16 peripherals. If CoreABC is connected to CoreAPB3, the settings for the APB Slot Size configuration options of these cores must match. For example, if CoreABC is configured for a slot size of 256 locations, CoreAPB3 must also have its slot size set to 256 locations. APB peripherals are accessed by APBWRT (to write to an APB peripheral) and APBREAD (to read from an APB peripheral). Both the slot number and the address within the slot must be specified in these instructions.

# **Registers**

### Accumulator

The accumulator (ACC) holds the result of data operations and is APB\_DWIDTH (8, 16, or 32) bits wide.

## **Z** Register (Optional)

The optional Z register (Z) is a general purpose register which may be used, for example, as a loop counter. The Z register is used to provide the address to the APB space when the APBREADZ and APBWRTZ instructions are executed. When present, the Z register is ZRWIDTH (1 to 16) bits wide.

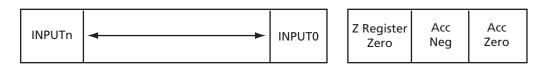

## Flags Register—Inputs and Condition Codes

CoreABC maintains a control register that is used in the conditional instructions; e.g., JUMP and CALL. This register cannot be read or used directly; instead, each named field can be used to control particular instructions. The Flags register has two sections, as shown in Figure 4-2.

Figure 4-2 • Flags and Inputs Register

There are three condition code type flags:

ZERO: Accumulator zero

NEGATIVE: Accumulator negative

ZZERO: Register zero

There are n INPUTS ( $n \le 28$ ), INPUT0 ... INPUT0, which are directly mapped to the general purpose inputs connected to CoreABC's IO\_IN[n:0] port. The number of these is configurable up to the lower of 28 or APB DWIDTH – 4, where APB DWIDTH is the width specified for the external APB data bus.

From these basic fields, other conditions are constructed and made available in the instruction set.

## **Instruction Set**

Table 4-1 through Table 4-8 on page 26 list the supported instructions. On the right hand side of these tables there are columns entitled Flags and Cycles. The Flags column contains two sub-columns, Acc. Zero and Acc. Neg., and the entries under these columns are either Yes or No. "Yes" indicates that the relevant flag, accumulator zero (Acc. Zero) or accumulator negative (Acc. Neg.), is affected by the instruction named in that row of the table. Similarly, a

"No" entry indicates that the flag is not affected by the instruction. The entries in the Cycles column give the number of (PCLK) clock cycles required for each instruction.

Table 4-1 • The Boolean and Arithmetic Instruction Group

|                             |                                                                                                                      | Fla       | Flags     |        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------|-----------|-----------|--------|

| Instruction <sup>1, 2</sup> | Description                                                                                                          | Acc. Zero | Acc. Neg. | Cycles |

| LOAD DAT Data               | Load accumulator with value.                                                                                         | Yes       | Yes       | 3      |

| LOAD RAM Address            | Load accumulator with value.                                                                                         | Yes       | Yes       | 3      |

| AND DAT Data                | Bitwise AND accumulator with immediate data.                                                                         | Yes       | Yes       | 3      |

| AND RAM Address             | Bitwise AND accumulator with RAM location.                                                                           | Yes       | Yes       | 3      |

| OR DAT Data                 | Bitwise OR accumulator with immediate data.                                                                          | Yes       | Yes       | 3      |

| OR RAM Address              | Bitwise OR accumulator with RAM location.                                                                            | Yes       | Yes       | 3      |

| XOR DAT Data                | Bitwise XOR accumulator with immediate data.                                                                         | Yes       | Yes       | 3      |

| XOR RAM Address             | Bitwise XOR accumulator with RAM location.                                                                           | Yes       | Yes       | 3      |

| INC                         | Increment accumulator.                                                                                               | Yes       | Yes       | 3      |

| DEC                         | Decrement accumulator.                                                                                               | Yes       | Yes       | 3      |

| ADD DAT Data                | Add immediate data to accumulator.                                                                                   | Yes       | Yes       | 3      |

| ADD RAM Address             | Add RAM location to accumulator.                                                                                     | Yes       | Yes       | 3      |

| SUB DAT Data                | Subtract immediate data from accumulator. SUB RAM is not supported.                                                  | Yes       | Yes       | 3      |

| MULT DAT Data               | Multiply accumulator by immediate data.  Core parameters determine multiplier return value.                          | Yes       | Yes       | 3      |

| MULT RAM Address            | Multiply accumulator by RAM location.  Core parameters determine multiplier return value.                            | Yes       | Yes       | 3      |

| CMP DAT Data                | Compare accumulator to immediate data.  ZERO set if equal; NEGATIVE set if MSBs differ.                              | Yes       | Yes       | 3      |

| CMP RAM Address             | Compare accumulator to RAM location.  ZERO set if equal; NEGATIVE set if MSBs differ.                                | Yes       | Yes       | 3      |

| CMPLEQ DAT Data             | Compare accumulator to immediate data.  ZERO set if equal; NEGATIVE set if ACC < Data.  CMPLEQ RAM is not supported. | Yes       | Yes       | 3      |

| SHL0                        | Shift accumulator left and infill with 0.                                                                            | Yes       | Yes       | 3      |

| SHR0                        | Shift accumulator right and infill with 0.                                                                           | Yes       | Yes       | 3      |

| SHL1                        | Shift accumulator left and infill with 1.                                                                            | Yes       | Yes       | 3      |

| SHR1                        | Shift accumulator right and infill with 1.                                                                           | Yes       | Yes       | 3      |

| SHLE                        | Shift accumulator left and infill with LSB.                                                                          | Yes       | Yes       | 3      |

| SHRE                        | Shift accumulator right and infill with MSB.                                                                         | Yes       | Yes       | 3      |

## Notes:

- 1. For most instructions, when using the configuration GUI, the DAT keyword can be omitted.

- 2. DAT may be replaced with DAT8 or DAT16 when only lower 8 or 16 data bits contain valid data. Using DAT8/DAT16 will reduce tile counts when instructions are held in logic tiles (that is, when the core is configured to operate in hard mode).

Table 4-1 • The Boolean and Arithmetic Instruction Group (continued)

|                             |                                                                                                                                 | Fla       | gs        |        |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|--------|

| Instruction <sup>1, 2</sup> | Description                                                                                                                     | Acc. Zero | Acc. Neg. | Cycles |

| ROL                         | Rotate accumulator left.                                                                                                        | Yes       | Yes       | 3      |

| ROR                         | Rotate accumulator right.                                                                                                       | Yes       | Yes       | 3      |

| BITCLR Data                 | Clear one bit in accumulator specified by argument (AND). In this case, the data value specifies the bit position.              | Yes       | Yes       | 3      |

| BITSET Data                 | Set one bit in accumulator specified by argument (OR). In this case, the data value specifies the bit position.                 | Yes       | Yes       | 3      |

| BITTST Data                 | Test one bit in accumulator. ZERO set if all requested bits are clear. In this case, the data value specifies the bit position. | Yes       | Yes       | 3      |

#### Notes:

- $1. \ \ For most instructions, when using the configuration GUI, the DAT keyword can be omitted.$

- 2. DAT may be replaced with DAT8 or DAT16 when only lower 8 or 16 data bits contain valid data. Using DAT8/DAT16 will reduce tile counts when instructions are held in logic tiles (that is, when the core is configured to operate in hard mode).

**Table 4-2** • The Memory Instruction Group

|                         |                                                                     | Flags     |           |        |

|-------------------------|---------------------------------------------------------------------|-----------|-----------|--------|

| Instruction             | Description                                                         | Acc. Zero | Acc. Neg. | Cycles |

| PUSH                    | Push the accumulator onto the stack.                                | No        | No        | 3      |

| PUSH ACC                | Push the accumulator onto the stack.                                | No        | No        | 3      |

| PUSH DAT Data           | Push immediate data onto stack.                                     | No        | No        | 3      |

| POP                     | Pop data from the stack to the accumulator and update the flags.    | Yes       | Yes       | 3      |

| RAMWRT Address ACC      | Write accumulator to RAM address.                                   | Yes       | Yes       | 3      |

| RAMWRT Address DAT Data | Write immediate data to RAM address.                                | Yes       | Yes       | 3      |

| RAMREAD Address         | Read data from RAM address to the accumulator and update the flags. | No        | No        | 3      |

Table 4-3 • The Z Register\* Instruction Group

|                |                                                                                                       | Fla       | ags       |        |

|----------------|-------------------------------------------------------------------------------------------------------|-----------|-----------|--------|

| Instruction    | Description                                                                                           | Acc. Zero | Acc. Neg. | Cycles |

| LOADZ ACC      | Load Z with accumulator.                                                                              | No        | No        | 3      |

| LOADZ DAT Data | Load Z with immediate value.                                                                          | No        | No        | 3      |

| ADDZ ACC       | Add accumulator to Z and store in Z. Only ZZERO flag is affected.                                     | No        | No        | 3      |

| ADDZ DAT Data  | Add immediate data to Z and store in Z. Only ZZERO flag is affected.                                  | No        | No        | 3      |

| SUBZ DAT Data  | Subtract immediate data from Z and store in Z. Only ZZERO flag is affected SUBZ ACC is not supported. | No        | No        | 3      |

| INCZ           | Increment Z. Only ZZERO flag is affected.                                                             | No        | No        | 3      |

| DECZ           | Decrement Z. Only ZZERO flag is affected.                                                             | No        | No        | 3      |

Note: \*The Z register is intended to be used as loop counter or APB address register.

Table 4-4 • The APB Instruction Group

|                              |                                                                                                       | Fla       | ags       |        |

|------------------------------|-------------------------------------------------------------------------------------------------------|-----------|-----------|--------|

| Instruction                  | Description                                                                                           | Acc. Zero | Acc. Neg. | Cycles |

| APBREAD Slot Address         | Read from APB.                                                                                        | No        | No        | 5      |

| APBWRT ACC Slot Address      | Write accumulator to APB at chosen address.                                                           | No        | No        | 5      |

| APBWRT ACM Slot Address      | Write value of ACM table, at location given by accumulator, to APB at chosen address.                 | No        | No        | 5      |

| APBWRT DAT Slot Address Data | Write data to chosen address.                                                                         | No        | No        | 5      |

| APBREADZ Slot                | Read from APB. The Z register specifies the APB address.                                              | No        | No        | 5      |

| APBWRTZ ACC Slot             | Write accumulator to APB. The Z register specifies the APB address.                                   | No        | No        | 5      |

| APBWRTZ ACM Slot             | Write value of ACM table, at location given by accumulator. The Z register specifies the APB address. | No        | No        | 5      |

| APBWRTZ DAT Slot Data        | Write data; the Z register specifies the APB address.                                                 | No        | No        | 5      |

Table 4-5 • The I/O Instruction Group

|                |                                                | Flags     |           |        |

|----------------|------------------------------------------------|-----------|-----------|--------|

| Instruction    | Description                                    | Acc. Zero | Acc. Neg. | Cycles |

| IOWRT ACC      | Write accumulator to I/O register.             | No        | No        | 3      |

| IOWRT DAT Data | Write data value to I/O register.              | No        | No        | 3      |

| IOREAD         | Load the accumulator with the I/O input value. | No        | No        | 3      |

**Table 4-6** • The Flow Control Instruction Group

|                                 |                                                                                                                                   | Fla       | ngs       |            |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------------|

| Instruction                     | Description                                                                                                                       | Acc. Zero | Acc. Neg. | Cycles     |

| JUMP Condition \$Label          | Jump to label.                                                                                                                    | No        | No        | 3          |

| JUMP IF/IFNOT Condition \$Label | Jump on condition to label.                                                                                                       | No        | No        | 3          |

| WAIT UNTIL/WHILE Condition      | Stop at this instruction until condition is TRUE.                                                                                 | No        | No        | 3          |

| CALL \$Label                    | As JUMP, but puts return address on stack.                                                                                        | No        | No        | 3          |

| CALL IF/IFNOT Condition \$Label | As JUMP, but puts return address on stack.                                                                                        | No        | No        | 3          |

| RETURN                          | Return from a CALL.                                                                                                               | No        | No        | 3          |

| RETURN IF/IFNOT Condition       | Return from a CALL on condition.                                                                                                  | No        | No        | 3          |

| RETISR Condition                | Return from an interrupt.                                                                                                         | No        | No        | 3          |

| RETISR IF/IFNOT Condition       | Return from an interrupt on condition.                                                                                            | No        | No        | 3          |

| HALT                            | Stop at this instruction. Interrupts will still be processed. HALT is a synonym for WAIT, and generally used without a condition. | No        | No        | Indefinite |

## Table 4-7 • Conditions for Flow Control Instruction Group

| Condition | Description                                                                  |  |

|-----------|------------------------------------------------------------------------------|--|

| ALWAYS    | Always. You can get the same effect as this by not specifying any condition. |  |

| ZERO      | Accumulator zero                                                             |  |

| NEGATIVE  | Accumulator negative                                                         |  |

| ZZERO     | Z register zero                                                              |  |

| INPUT0    | Input0 set                                                                   |  |

| INPUT1    | Input1 set and similarly for higher Inputs, if available.                    |  |

| POSITIVE  | Equivalent to NOT NEGATIVE                                                   |  |

| LTE_ZERO  | Less than or equal to zero; the combination NEGATIVE OR ZERO                 |  |

| GT_ZERO   | Greater than zero; the combination NOT (NEGATIVE OR ZERO)                    |  |

### Table 4-8 • Other Instructions

|             |              | Flags     |           |        |

|-------------|--------------|-----------|-----------|--------|

| Instruction | Description  | Acc. Zero | Acc. Neg. | Cycles |

| NOP         | No operation | No        | No        | 3      |

# 5 - CoreABC Operation

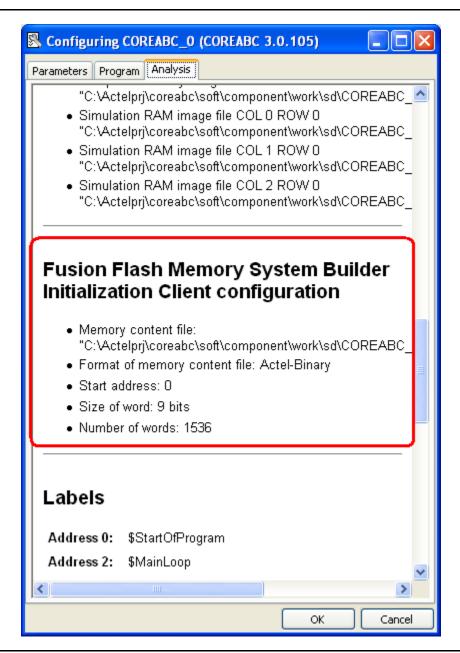

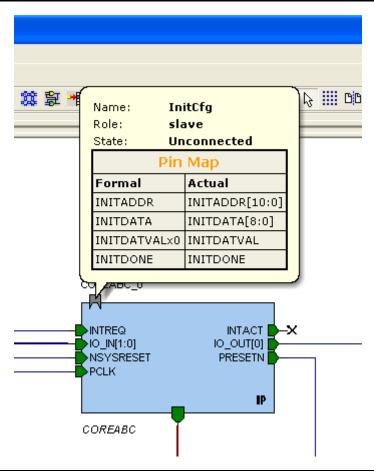

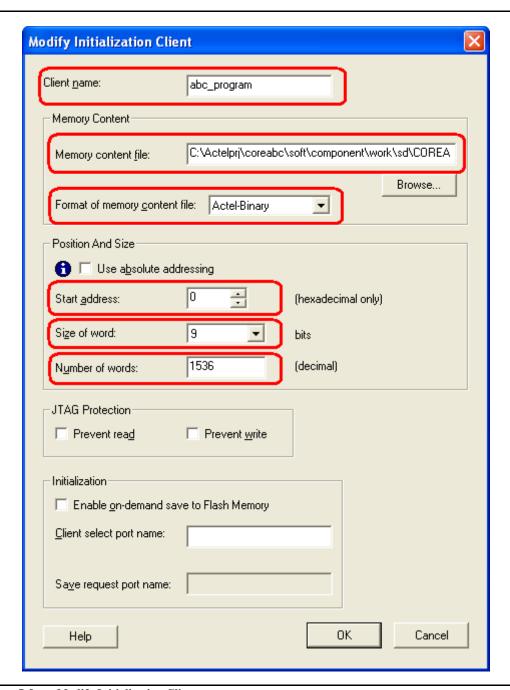

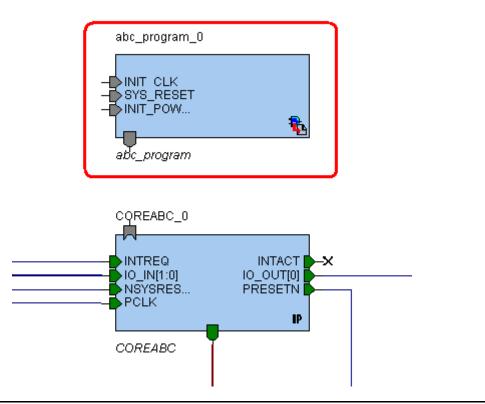

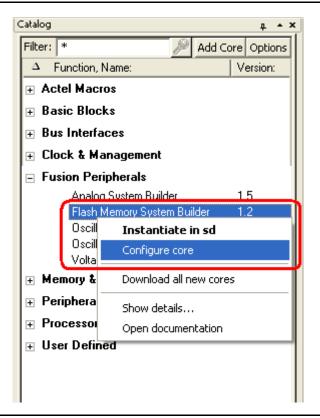

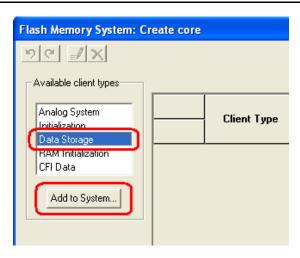

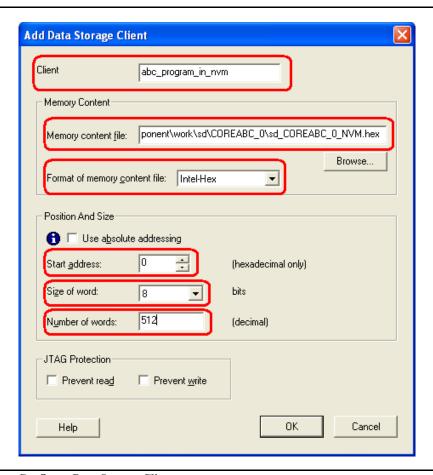

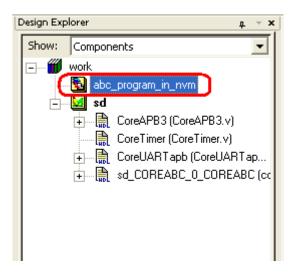

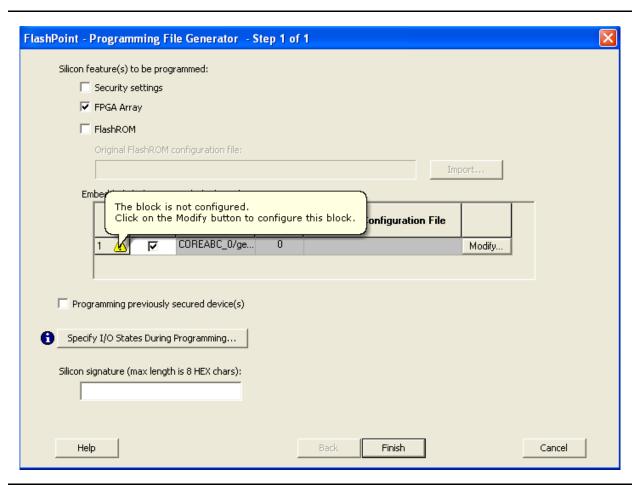

# **ACM Lookup Table for Use with CoreAI**